- #How to open after i download xilinx ise software full

- #How to open after i download xilinx ise software verification

- #How to open after i download xilinx ise software software

- #How to open after i download xilinx ise software windows 7

Make sure that the Create Project Subdirectory box is checked. Enter tutorial in the Project name field. Click the Browse button of the Project location field of the New Project form, browse to c:\xup\digital, and click Select.ġ-1-4. Nexys3 PlanAhead Tutorial-3 copyright 2013 Xilinxġ-1-3. You will see Create A New PlanAhead Project dialog box.

Click Create New Project to start the wizard.

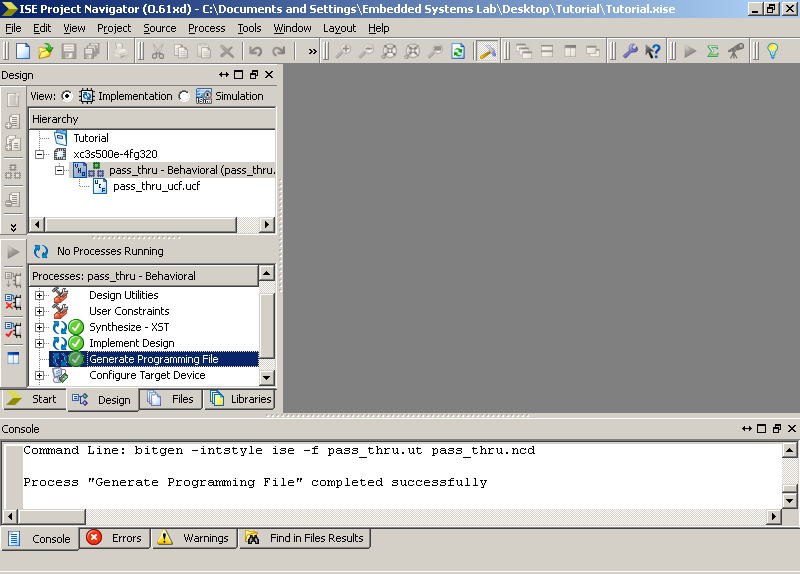

Open PlanAhead by selecting Start > All Programs > Xilinx Design Tools > ISE Design Suite 14.6 > PlanAhead > PlanAhead.ġ-1-2. Use the provided tutorial.v and tutorial.ucf files in the sources directory.ġ-1-1. Launch PlanAhead and create a project targeting the xc6slx16csg324-2 device and using the Verilog HDL. General Flow for this tutorial Create a PlanAhead project and analyze source files Simulate the design using ISim simulator Synthesize the design Implement the design Perform the timing simulation Verify the functionality in hardware using Nexys3ġ-1. Other inputs are logically operated on before the results are output on the remaining LEDs as shown in Figure 1. The design consists of some inputs directly connected to the corresponding output LEDs. Nexys3 PlanAhead Tutorial-2 copyright 2013 Xilinx Follow these detailed instructions to progress through the tutorial. This tutorial is broken into steps that consist of general overview statements providing information on detailed instructions that follow. The Nexys3 board Use the provided user constraint file (UCF) to constrain pin locations Simulate the design using the ISim simulator Synthesize and implement the design Generate the bitstream Configure the Spartan-6 FPGA with the generated bitstream and verify the functionality The circled number indicates the corresponding step in this tutorial.Īfter completing this tutorial, you will be able to: Create a PlanAhead project sourcing HDL model(s) and targeting a specific FPGA device located on You will go through the typical design flow targeting the Spartan-6 based Nexys3 board. A typical design flow consists of creating model(s), creating user constraint file(s), creating a PlanAhead project, importing the created models, assigning created constraint file(s), optionally running behavioral simulation, synthesizing the design, implementing the design, generating the bitstream, and finally verifying the functionality in the hardware by downloading the generated bitstream file.

#How to open after i download xilinx ise software software

This tutorial guides you through the design flow using Xilinx PlanAhead software to create a simple digital circuit using Verilog HDL.

#How to open after i download xilinx ise software full

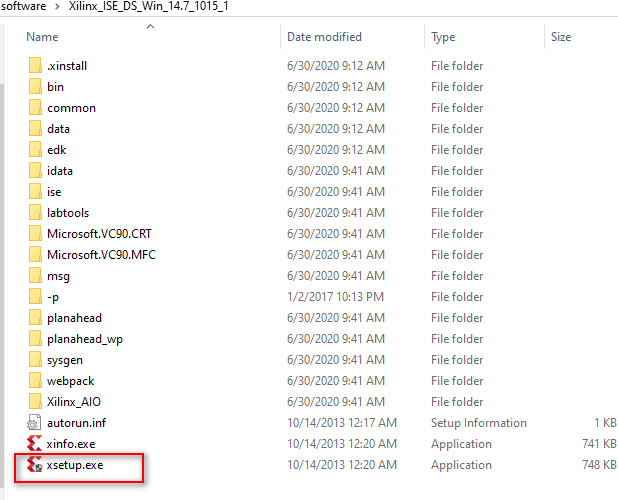

However, a paid license is required for this version to use and gives the benefit of full functionality, in deference to the web edition.Nexys3 PlanAhead Tutorial-1 copyright 2013 Xilinx The subscription edition of Xilinx ISE is available on their website for download.

#How to open after i download xilinx ise software verification

Key features in the edition include the following: embedded processing design support for Zynq-7000 All Programmable SoC family the Z-7010, Z-7020, Z-7030 integrated HDL verification with the lite version of the ISE Simulator (ISim) complete front-to-back design environment, with a full plan ahead and analysis tool and many others.

#How to open after i download xilinx ise software windows 7

The software is compatible for Linux, Windows XP, and Windows 7 systems. This free version offers only limited programming and synthesis for devices in contrast to the subscription edition of Xilinx ISE that has full access to capabilities. The Xilinx ISE (Integrated Software Environment) WebPack Design software is a free development environment for designing FPGA (Field-Programmable Gate Array) and CPLD (Complex Programmable Logic Device) with an HDL (Hardware Description Language) synthesis and simulation, implementation, device fitting, and JTAG (Joint Test Action Group) programming.

0 kommentar(er)

0 kommentar(er)